File list

From gem5

This special page shows all uploaded files.

First page |

Previous page |

Next page |

Last page |

| Date | Name | Thumbnail | Size | User | Description | Versions |

|---|---|---|---|---|---|---|

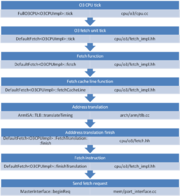

| 13:02, 9 July 2012 | Fetch.png (file) |  |

180 KB | Wilwan01 | O3 CPU fetch flow | 1 |

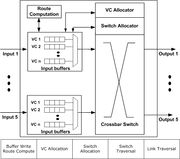

| 12:23, 1 April 2011 | Garnet router.jpg (file) |  |

47 KB | Tushar | Router Microarchitecture and Pipeline modeled in Garnet. | 1 |

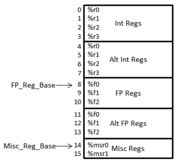

| 01:21, 31 July 2013 | Gem5-regs.png (file) |  |

11 KB | Stever | 2 | |

| 18:18, 17 January 2013 | Gem5 ARM Streamline -Timeline.png (file) |  |

276 KB | Dsunwoo | 1 | |

| 16:42, 14 February 2012 | Gem5 initialization call sequence.png (file) |  |

58 KB | Plafratt | Figure showing function call sequence during the initialization of gem5. | 1 |

| 14:43, 3 December 2012 | Gem5 user workshop intro.pdf (file) | 309 KB | Saidi | 1 | ||

| 09:44, 12 December 2012 | Gem5 workshop arm soc exploration ext.pdf (file) | 1.3 MB | Alex romana | 1 | ||

| 09:44, 12 December 2012 | Gem5 workshop systemC integration ext.pdf (file) | 856 KB | Alex romana | 1 | ||

| 14:58, 3 December 2012 | Gutierrez gem5 workshop 2012.pdf (file) | 772 KB | Saidi | 1 | ||

| 19:40, 29 August 2018 | Gutierrez hpca 2018 lost in abstraction.pdf (file) | 609 KB | Atgutier | 1 | ||

| 12:24, 1 April 2011 | Interconnection network.jpg (file) |  |

38 KB | Tushar | Interconnection Network High-Level figure | 1 |

| 12:50, 5 July 2017 | Isca2017-dist-gem5.pdf (file) | 2.24 MB | Andysan | Slides from the ISCA2017 dist-gem5 tutorial. | 1 | |

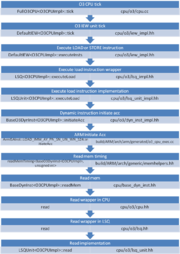

| 13:03, 9 July 2012 | LDSTR.png (file) |  |

284 KB | Wilwan01 | O3 CPU Load/Store flow | 1 |

| 22:08, 25 March 2011 | MI example cache FSM.jpg (file) |  |

97 KB | Rsen | FSM for the cache controller for MI_example coherence protocol. | 1 |

| 21:28, 26 March 2011 | MI example dir FSM.jpg (file) |  |

113 KB | Rsen | updated FSM to include transition on PUTX. | 2 |

| 07:51, 27 March 2011 | MOESI CMP directory L1cache FSM.jpg (file) |  |

207 KB | Rsen | FSM for L1 cache controller for MOESI_CMP_directory coherence protocol. | 1 |

| 09:41, 27 March 2011 | MOESI CMP directory L1cache optim FSM.jpg (file) |  |

90 KB | Rsen | FSM for L1 cache controller optimizations (SM, OM states) for MOESI_CMP_directory coherence protocol. | 1 |

| 10:21, 3 April 2011 | MOESI CMP directory L2cache FSM part 1.jpg (file) |  |

333 KB | Rsen | moved position of the {ILOS -> OLS} transition annotation. | 3 |

| 13:33, 3 April 2011 | MOESI CMP directory L2cache FSM part 2.jpg (file) |  |

200 KB | Rsen | FSM (part 2) of the L2 cache controller for the MOESI_CMP_directory cache coherence protocol. | 1 |

| 23:36, 26 March 2011 | MOESI CMP directory dir FSM.jpg (file) |  |

152 KB | Rsen | Corrected transitions from I on GETS. | 2 |

| 00:00, 31 March 2011 | MOESI hammer cache FSM.jpg (file) |  |

62 KB | Somayeh | 1 | |

| 01:00, 1 April 2011 | MOESI hammer dir FSM.jpg (file) |  |

46 KB | Somayeh | 1 | |

| 20:12, 31 March 2011 | Mc addr command timing.jpg (file) | 45 KB | Rsen | Timing diagram of address and command signals for the Memory controller. This figure was created by Andy Phelps in 2008. | 1 | |

| 21:16, 31 March 2011 | Mc addr command timing back to back.jpg (file) | 52 KB | Rsen | Timing diagram for back-to-back command and address sequences for the Memory Controller. The figure was created by Andy Phelps in 2008. | 1 | |

| 19:36, 31 March 2011 | Mc data struct.jpg (file) |  |

79 KB | Rsen | High level view of memory controller data structures. Adapted from a figure created by Andy Phelps in 2008. | 1 |

| 06:32, 25 March 2011 | Mc overview.jpg (file) |  |

159 KB | Rsen | High level overview of Memory Controller and memory organization. | 1 |

| 14:08, 16 July 2011 | O3pipeview.png (file) |  |

75 KB | Saidi | 1 | |

| 11:02, 7 June 2017 | Packet-forwarding-highlevel.png (file) |  |

361 KB | Rjagtap | 1 | |

| 14:42, 6 December 2012 | Performance Prediction Models gem5 workshop.pdf (file) | 1.95 MB | Saidi | 1 | ||

| 15:42, 19 March 2011 | Ruby overview.jpg (file) |  |

96 KB | Rsen | Reverted to version as of 19:36, 19 March 2011 | 4 |

| 12:22, 1 April 2011 | Simple network.jpg (file) |  |

12 KB | Tushar | Simple Network Figure from GEMS ISCA tutorial | 1 |

| 20:28, 24 March 2011 | Slicc overview.jpg (file) | 116 KB | Rsen | Added a FSM picture for the state machine. Both components of the picture appear in the GEMS tutorial in ISCA 2005. | 2 | |

| 14:41, 10 September 2017 | Summit2017 COSSIM.pdf (file) | 847 KB | Andysan | 1 | ||

| 04:47, 11 September 2017 | Summit2017 Intro to gem5.pdf (file) | 1.27 MB | Andysan | 1 | ||

| 14:40, 10 September 2017 | Summit2017 complex fs incorporating accelerators.pdf (file) | 1.16 MB | Andysan | 1 | ||

| 07:51, 6 November 2017 | Summit2017 drampower.pdf (file) | 319 KB | Andysan | 1 | ||

| 10:26, 9 November 2017 | Summit2017 elasticsimmate.pdf (file) | 6.11 MB | Andysan | 1 | ||

| 07:29, 11 September 2017 | Summit2017 garnet2.0 tutorial.pdf (file) | 2.12 MB | Andysan | 1 | ||

| 10:49, 11 September 2017 | Summit2017 learning gem5 ruby.pdf (file) | 1.69 MB | Andysan | 1 | ||

| 10:23, 8 November 2017 | Summit2017 powerframework.pdf (file) | 420 KB | Andysan | 1 | ||

| 14:47, 10 September 2017 | Summit2017 powmon.pdf (file) | 3.3 MB | Andysan | 1 | ||

| 07:50, 6 November 2017 | Summit2017 starterkit.pdf (file) | 1.62 MB | Andysan | 1 | ||

| 12:45, 11 September 2017 | Summit2017 systemc.pdf (file) | 2.93 MB | Andysan | 1 | ||

| 07:47, 6 November 2017 | Summit2017 trace generation.pdf (file) | 554 KB | Andysan | 1 | ||

| 06:52, 11 September 2017 | Summit2017 wa devlib.pdf (file) | 918 KB | Andysan | 1 | ||

| 13:07, 16 March 2012 | TimingSimpleCPU.jpg (file) |  |

131 KB | Mat2909 | 1 | |

| 21:50, 21 March 2011 | Topology overview.jpg (file) | 168 KB | Rsen | High-level picture of various well-known topologies. Individual components were taken from the GEMS tutorial in ISCA 2005. | 1 | |

| 06:32, 10 December 2015 | Trace cpu detail.jpg (file) |  |

188 KB | Rjagtap | 1 | |

| 06:29, 10 December 2015 | Trace cpu top level.jpg (file) |  |

73 KB | Rjagtap | 1 | |

| 03:40, 4 December 2012 | Tsinghua's Presentation for gem5 Workshop 2012.pdf (file) | 5.14 MB | Saidi | 1 |

First page |

Previous page |

Next page |

Last page |