## AMD'S gem5 APU SIMULATOR ✓

AMD RESEARCH JUNE 14, 2015

## **OVERVIEW**

- ✓ Introducing AMD's gem5 APU Simulator

- Extends gem5 with a GPU timing model

- Supports Heterogeneous System Architecture in SE mode

- Includes several Ruby-based APU memory systems

- This talk

- Heterogeneous System Architecture

- Execution flow

- Release schedule

- ▲ Future plans

## WHAT IS HSA? HETEROGENEOUS SYSTEM ARCHITECTURE

**Processor design** that makes it easy to harness the entire computing power of an APU for faster and more power-efficient devices, including personal computers, tablets, smartphones, and cloud servers

## HSA BUILDING BLOCKS

http://hsafoundation.com

http://github.com/HSAFoundation

## **HSA Hardware Building Blocks**

- Shared Virtual Memory

- Single address space

- Coherent

- Pageable

- Fast access from all components

- Can share pointers

- ▲ Architected User-Level Queues

- ✓ Signals

- Context Switching

- Platform Atomics

- Defined Memory Model

## **HSA Software Building Blocks**

- HSAILPortable, parallel, compiler IR

- Instruction definition

▲ HSA Runtime

**HSA Platform**

System Arch

**Specification**

- Create queues

- Allocate memory

- Device discovery

- Multiple high level compilers

- CLANG/LLVM/HSAIL

- C++, OpenMP, OpenACC, Python

Industry standard, architected requirements for how devices share memory and communicate with each other

Industry standard compiler IR and runtime to enable existing programming languages to target the GPU

### **APU SIMULATION SUPPORT**

## **HSA Hardware Building Blocks**

- Shared Virtual Memory

- Single address space

- Coherent

- Pageable

- Fast access from all components

- Can share pointers

- **Architected User-Level Queues**

- Signals

- **Context Switching**

- **Platform Atomics**

- **Defined Memory Model**

## **HSA Software Building Blocks**

- **HSAIL**

- Portable, parallel, compiler IR

- Instruction definition

- HSA Runtime (OpenCL<sup>TM</sup> Runtime)

- Create queues

- Allocate memory

- Device discovery

- Multiple high-level compilers

- CLANG/LLVM/HSAIL

- C++, OpenMP, OpenACC, Python

#### Legend

Included in first release

Work-in-progress / may be released

Longer term work

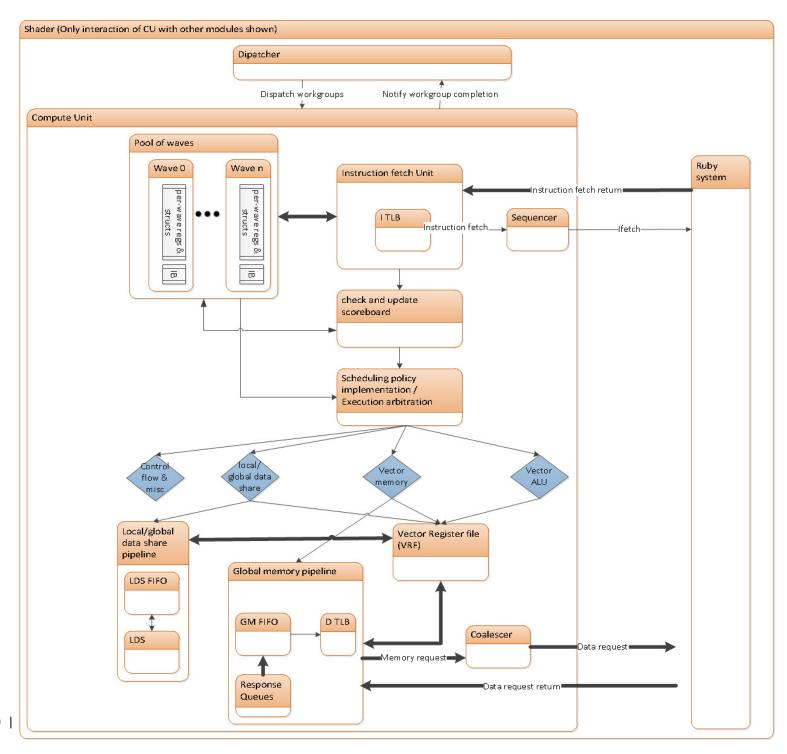

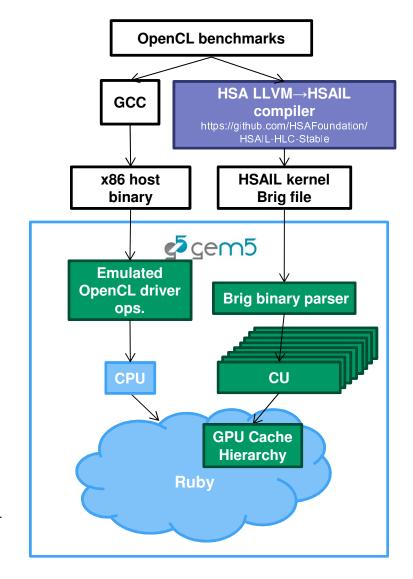

## APU SIMULATION FLOW

- - w/ AMD added components

- Supports HSAIL/BRIG kernels

- System emulation simulation

- No OS or device driver

- Execution-driven evaluation

- GPU directly executes HSAIL

- CPU executes x86

#### Details

- GCN GPU model\*

- Multiple GPU cache hierarchies

- Write-through

- Read-for-ownership

[\*] AMD Graphics Core Next (GCN) Architecture, White Paper. http://www.amd.com/Documents/GCN Architecture whitepaper.pdf. June 2012.

## RELEASE SCHEDULE

- ▲ First patches posted for review on May 11

- We appreciate the active discussion and reviews.

- We made many, many modifications based on reviewer feedback

- Please keep the "cost/benefit" analysis in mind when asking for changes

## **AMD**

# Questions?

## **DISCLAIMER & ATTRIBUTION**

The information presented in this document is for informational purposes only and may contain technical inaccuracies, omissions and typographical errors.

The information contained herein is subject to change and may be rendered inaccurate for many reasons, including but not limited to product and roadmap changes, component and motherboard version changes, new model and/or product releases, product differences between differing manufacturers, software changes, BIOS flashes, firmware upgrades, or the like. AMD assumes no obligation to update or otherwise correct or revise this information. However, AMD reserves the right to revise this information and to make changes from time to time to the content hereof without obligation of AMD to notify any person of such revisions or changes.

AMD MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE CONTENTS HEREOF AND ASSUMES NO RESPONSIBILITY FOR ANY INACCURACIES, ERRORS OR OMISSIONS THAT MAY APPEAR IN THIS INFORMATION.

AMD SPECIFICALLY DISCLAIMS ANY IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR ANY PARTICULAR PURPOSE. IN NO EVENT WILL AMD BE LIABLE TO ANY PERSON FOR ANY DIRECT, INDIRECT, SPECIAL OR OTHER CONSEQUENTIAL DAMAGES ARISING FROM THE USE OF ANY INFORMATION CONTAINED HEREIN, EVEN IF AMD IS EXPRESSLY ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

#### **ATTRIBUTION**

© 2015 Advanced Micro Devices, Inc. All rights reserved. AMD, the AMD Arrow logo and combinations thereof are trademarks of Advanced Micro Devices, Inc. in the United States and/or other jurisdictions. SPEC is a registered trademark of the Standard Performance Evaluation Corporation (SPEC). OpenCL is a trademark of Apple Inc. used by permission by Khronos. Other names are for informational purposes only and may be trademarks of their respective owners.